Memorie

Le memorie sono dispositivi che consentono di immagazzinare e di mantenere,

in modo permanente o temporaneo, informazioni espresse in forma binaria.

Nei sistemi a logica cablata

le memorie sono usate prevalentemente come generatori di caratteri o

convertitori di codice o registri per la memorizzazione temporanea di dati.

Nei sistemi a logica programmabile vengono usate per memorizzare il programma,

ossia la sequenza delle istruzioni necessarie per lesecuzione di un determinato

processo di elaborazione e per immagazzinare dati da elaborare, i risultati

intermedi ed i risultati finali.

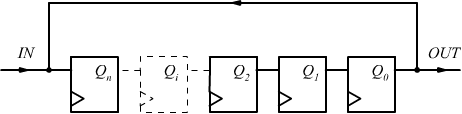

Una prima classificazione delle memorie può essere fatta in base a quella che è la modalità di accesso al dispositivo; cioè al modo con cui i dati vengono prelevati ed immagazzinati; si distinguono allora principalmente le memorie ad accesso sequenziale da quelle ad accesso diretto o casuale (random).

Le prime sono essenzialmente costituite da uno o più registri a scorrimento, dotati di terminali per la lettura e la scrittura ed eventualmente da un anello per la ricircolazione dei dati.

Nelle memorie ad accesso casuale è invece possibile accedere direttamente a qualsiasi dato indipendentemente dalla posizione in cui esso si trova.

All'interno delle memorie ad accesso casuale vi è una ulteriore classificazione

che consiste nel distinguere le memorie volatili da quelle non volatili,

nelle prime la memorizzazione dei dati è solo temporanea, nelle seconde

è permanente.

Nelle memorie volatili l'utilizzatore può, con procedura molto semplice

e veloce, scrivere e leggere dati durante una fase di elaborazione finchè

il sistema è alimentato elettricamente; se viene tolta l'alimentazione,

le informazioni memorizzate vanno perdute.

Di questa classe di memorie fa parte la RAM (Random Access Memory) di lettura

e scrittura.

Le memorie non volatili mantengono l'informazione in modo stabile per un tempo illimitato e possono essere persino rimosse dal sistema in cui sono inserite per essere usate in un altro sistema. A questa categoria appartengono le ROM (Read Only memory).

Memoria ad accesso casuale

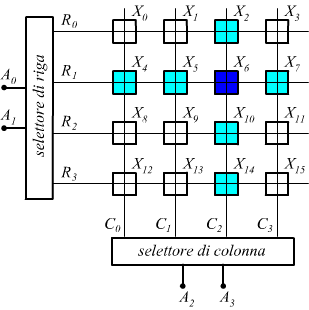

Le celle di memoria, sono in questo caso, disposte in strutture a matrice di tipo unidimensionali o più spesso di tipo bidimensionale.

La posizione di ogni cella è definita dalle sue coordinate, cioè dal numero

di riga e di colonna che in essa si intersecano.

Ad esempio, per indirizzare le 16 celle dello schema sopra disegnato sono

necessarie otto linee, quattro orizzontali e quattro verticali controllate

da opportuni selettori (decodificatori) di riga e di colonna le linee di

ingresso dei selettori A0A1 ed A2A3

consentono di attivare una sola riga ed un sola colonna per volta e quindi

di selezionare una cella per volta. quindi i valori presenti sulle linee

A0A1A2A3 costituiscono gli indirizzi

di ciascuna cella o locazione di memoria.

In questo esempio, per accedere alla locazione 6 occorre individuare la

seconda riga per mezzo del numero binario A0A1=01

e la terza colonna A2A3=10.

Ipotizzando che ogni locazione di memoria possa contenere 1 byte=8 bit, l'intera memoria può essere rappresentata con il seguente simbolo:

Le operazioni di lettura/scrittura sono distinte da un selettore ![]() .

.

Per leggere il dato in tale locazione si pone alto il valore dell'input

![]() (

lo si pone basso se si vuole scrivere nella stessa locazione) e dopo un

intervallo di tempo che tiene conto della dei ritardi della logica di comando,

il dato sarà disponibile sulle linee di uscita.

(

lo si pone basso se si vuole scrivere nella stessa locazione) e dopo un

intervallo di tempo che tiene conto della dei ritardi della logica di comando,

il dato sarà disponibile sulle linee di uscita.

Nel disegno si vedono oltre alle linee degli indirizzi anche le linee dati

(IN/OUT) caratterizzate dal loro numero, non ci è quindi difficile immaginare

come possa venir gestita la singola locazione di memoria, vale a dire, con

un sistema di input/output simile a quello dei registri

con lettura e scrittura in parallelo.

In questo caso il fronte attivo dell'impulso di clock costituisce il segnale di scrittura che permette di avere direttamente disponibili i valori scritti sui terminali di uscita.

Organizzazione di memoria

Nella struttura di memoria a matrice sopra disegnata, ciascuna combinazione di valori delle linee di indirizzo A3÷A0 seleziona una delle 16 celle (o anche una delle 16 locazioni di memoria). L'organizzazione della memoria è definita come il numero di locazioni per il valore in bit di ogni locazione

![]()

nloc=numero delle locazioni di memoria

m=parola=numero di bit che possono essere contenuti in una locazione

In questo caso si dice che la memoria è organizzata in 16 parole (locazioni)

di 8 bit ciascuna .

![]()

Capacità di memoria

Una delle caratteristiche più importanti di una memoria è la sua capacità,

cioè il numero di bit che essa può contenere.

Poiché l'indirizzamento delle locazioni di memoria è basato sul codice binario,

i valori di capacità sono di solito delle potenze del 2 come 64, 256, 512,

1024 bit (..etc.).

Considerando poi che in molti sistemi il trasferimento di un dato alla memoria

interessa un gruppo di 8 bit(=1byte) la capacità della memoria è misurata

prevalentemente in byte.

Da quello che si vede nel nostro caso si hanno 16 locazioni (nloc) di memoria e n=4 linee di indirizzo, si ha la relazione

![]()

• nloc=numero delle locazioni di memoria

• m=parola=numero di bit che possono essere contenuti in una locazione

• n=numero delle linee di indirizzamento

E' possibile conoscere la capacità C di una memoria

![]()

Se come ipotizziamo stiamo usando un sistema ad 8 bit si ha m=8 la capacità sarà C=24·8=128 bit o 16byte (128/8=16).

Quantità di memoria

Immaginiamo una memoria con organizzazione

org=1024×8=1k×8

questa identifica una matrice RAM che memorizza un totale di 8196 bit,

suddivisi in 1024 locazioni, da 8 bit ciascuno.

Esistono 10 linee d'indirizzo, perché 210=1024.

Questa matrice memorizza 1024 byte. Questa quantità viene chiamata kilobyte (dal greco Khilioi, che significa mille) viene utilizzato soprattutto nel sistema metrico, per esempio un chilogrammo equivale a 1000 grammi; un chilometro equivale 1000 metri. Ma, come abbiamo visto, 1 kilobyte=1024 byte e non vale 1000 byte.

Il problema è che il sistema metrico è basato sulle potenze del 10, mentre i numeri binari si basano sulle potenze del 2. Le potenze del 10 sono 10,100,1000 etc. , le potenze del 2 sono 2,4,8,16,32,64,etc.

Non esistono potenze intere del 10 che coincidono con potenze intere del 2. Tuttavia, di tanto in tanto, i due percorsi si avvicinano tra loro. In effetti, 1000 è abbastanza vicino a 1024 .

210≈1000=103 k o kb

Il simbolo ≈ significa 'approssimativamente'.

Se la matrice precedente memorizza 1024 byte o 1 kilobyte o 1k o 1kb

1 kilobyte=1024 byte= 210byte ≈103 byte

2 kilobyte=2048 byte= 211byte

4 kilobyte=4096 byte= 212byte

8 kilobyte=8192 byte= 213byte

16 kilobyte=16384 byte= 214byte

32 kilobyte=32768 byte= 215byte

64 kilobyte=65536 byte= 216byte

128 kilobyte=131032 byte= 217byte

256 kilobyte=262144 byte= 218byte

512 kilobyte=524288byte= 219byte

1024 kilobyte=1048.576byte= 220byte≈ 106byte

notare come i numeri di kilobyte riportati a sinistra, siano anche potenze

di 2.

Secondo la stessa logica che consente di indicare la quantità 1024 byte come un kilobyte, ci si può riferire a 1024 kilobyte con il termine megabyte (la parola greca megas significa enorme). La forma abbreviata di megabyte è Mb, e il raddoppio di memoria prosegue:

1 megabyte = 1.048.576 byte = 220 byte ≈ 106byte

2 megabyte = 2.097.152 byte = 221 byte

4 megabyte = 4.194.304 byte = 222 byte

8 megabyte = 8.388.608 byte = 223 byte

16 megabyte = 16.777.216 byte = 224 byte

32 megabyte = 33.554.432 byte = 225 byte

64 megabyte = 67.108.864 byte = 226 byte

128 megabyte = 134.217.728 byte = 227 byte

256 megabyte = 268.435.456 byte = 228 byte

512 megabyte = 536.870.912 byte = 229 byte

1024 megabyte = 1.073.741.824 byte = 230 byte ≈ 109

byte

la parola greca gigas significa gigante, quindi 1024 megabyte vengono definiti un gigabyte, abbreviato in Gb.

In modo analogo, un terabyte ( teras significa mostro) equivale a 240 byte (approssivamente 1012 ) o 1.099.511.627.776 byte.Terabyte è abbreviato in Tb.

Un kilobyte equivale all'incirca a 1000 byte, un megabyte è circa un milione di byte, un gigabyte è approssivamente uguale ad un miliardo di byte e un terabyte equivale circa ad un trilione di byte.

Immaginando che le quantità di memoria a disposizione degli elaboratori possano ulteriormente aumentate in futuro, dovremo abituarci ad usare altre unità di misura.

Un petabyte (Pb) equivale alla 250 byte ed quivale a 1.125.899.906.842.624 byte che è uguale a circa a 1015 o ad un quatrilione.

Un exabyte (Eb) equivale a 260 byte o 1.152.921.504.606.846.976, approssimativamente 1018 o un quintilione.

Dopo questo delirio di numeri si può solo sottolineare che quando si parla di memoria, le quantità si esprimono quasi sempre in byte e non in bit (1byte=8bit). In genere, i kilobit o megabit vengono citati in un contesto che coinvolge la trasmissione di dati via cavo (cioè quando ci vogliono vendere una linea internet) e il più delle volte appaiono in espressioni come "kilobit al secondo" o "megabit al secondo".

linee dati e linee degli indirizzi

Per consentire la lettura/scrittura sono necessarie oltre alle linee degli

indirizzi le linee dati. In una memoria a sola lettura le linee dati sono

linee di uscita in numero pari a quello dei bit di ciascuna locazione di

memoria. Nelle memorie a lettura/scrittura è anche necessario un terminale

di controllo che selezioni con un suo valore alto o basso, rispettivamente

l'operazione di lettura o scrittura![]() (read/write)

.

(read/write)

.

Per il trasferimento dei dati occorrono poi linee di ingresso per la scrittura

e line di uscita per la lettura ma in pratica,nella stragrande maggioranza

delle memorie integrate viene usato lo stesso terminale per l'ingresso e

per l'uscita dei dati.

In tutte le memorie è presente un terminale aggiuntivo CS

(Chip Select) che quando è posto al suo livello attivo abilita il

dispositivo.

In questo disegno è rappresentata una RAM ma dobbiamo ricordarci che lo stesso schema potrebbe rappresentare una ROM a patto di cancellare le linee di input (nelle ROM non si può scrivere).

Moduli di memoria

Nella progettazione di sistemi digitali è molto frequente l'esigenza di realizzare moduli o banchi di memoria con capacità maggiore ed organizzazione diversa. A questo fine occorre combinare più chip per ampliare il numero di bit per parola oppure per aumentare il numero di parole disponibili.

Espansione della larghezza di parola

Supponiamo di usare dei chip con 8 parole (locazioni) da 4 bit ciascuna

; per ogni singolo chip vi dovranno essere 3 linee per gli indirizzi (8=23

).

Volendo ottenere una memoria sempre con 8 parole ma con 8 bit per ciascuna

parola, possiamo disporre due chip di questo tipo in parallelo come segue

Si nota come i tre bit di indirizzo debbano essere applicati agli ingressi

di entrambi i dispositivi, cosi come i segnali di selezione CS e di lettura/scrittura

![]() . La

memoria M0 accetta e mantiene i 4 bit meno significativi, mentre M1 memorizza

gli altri 4. Questo tecnica può essere applicata per ottenere parole con

un numero di bit maggiore (12, 16 , etc.).

. La

memoria M0 accetta e mantiene i 4 bit meno significativi, mentre M1 memorizza

gli altri 4. Questo tecnica può essere applicata per ottenere parole con

un numero di bit maggiore (12, 16 , etc.).

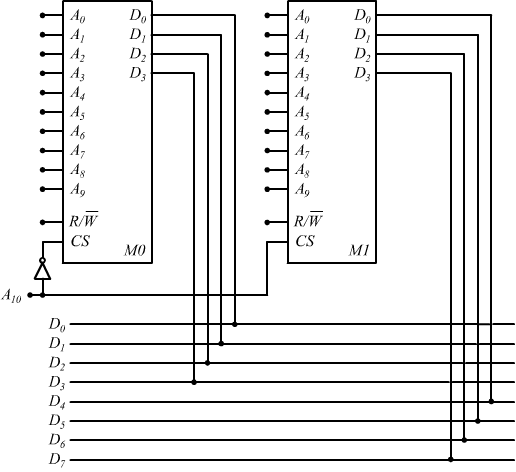

Un altro esempio in scala maggiore è il seguente dove si possono notare

due banchi di RAM con organizzazione 1k×4 ciascuno

La connessione effettuata consente di espandere la linea dati da 4 ad 8 e di ottenere una memoria equivalente 1k×8. Lo stesso indirizzo permette la lettura o la scrittura di una stessa locazione nelle due memorie mentre le linee dei dati delle due memorie sono connesse in modo tale che le due parole da 4 bit vadano a costituire una sola parola da 8 bit.

Espansione di memoria in banchi

Sempre nell'ipotesi di usare dei chip con 8 parole da 4 bit e di voler ottenere, invece, una memoria con 16 parole sempre da 4 bit, bisogna pensare che : 16=24 cioè, sono necessarie 4 linee per gli indirizzi.

Le prime tre linee A2A1A0 vengono applicate

ad entrambi i chip; la terza linea, controllerà l'ingresso di selezione

CS in modo che

se A3=0 viene abilitato M0

se A3=1 viene abilitato M1

Quindi gli indirizzi da A3A2A1A0=0000 a A3A2A1A0=0111 selezionano le 8 locazioni di M0.

Gli indirizzi da A3A2A1A0=1000

a A3A2A1A0=1111 selezionano

le 8 locazioni di M1. I bit di input-output D3D2D1D0

sono applicati ad entrambi i banchi come il segnale di lettura - scrittura

![]() .

In generale, l'espansione della memoria può avvenire in due modi:

.

In generale, l'espansione della memoria può avvenire in due modi:

1) si espande il numero delle linee di dati

2) si espande il numero delle linee di indirizzo

Un altro esempio in scala molto maggiore: avendo a disposizione banchi di memoria con org=1k×8 realizzare una memoria complessiva di 2k.

Ogni banco contiene 1024 locazioni da 8 bit ciascuna. I due dispositivi sono connessi alle stesse otto linee dati D7÷D0 e alle stesse dieci linee di indirizzo A9÷A0 . E' stata, però, introdotta, una supplementare linea di indirizzo A10 che abilita il primo banco quando A10=0 ed abilita il secondo banco a destra quando A10=1. Gli indirizzi sono i seguenti:

indirizzo della prima locazione di memoria del 1°banco

A10A9A8A7A6A5A4A3A2A1A0 = 000.0000.0000

A10A9A8A7A6A5A4A3A2A1A0 = 011.1111.1111 =(3FF)H

indirizzo della prima locazione di memoria del 2°banco

A10A9A8A7A6A5A4A3A2A1A0 = 100.0000.0000 =(400)H

indirizzo dell'ultima locazione di memoria del 2°banco

A10A9A8A7A6A5A4A3A2A1A0 = 111.1111.1111 =(7FF)H

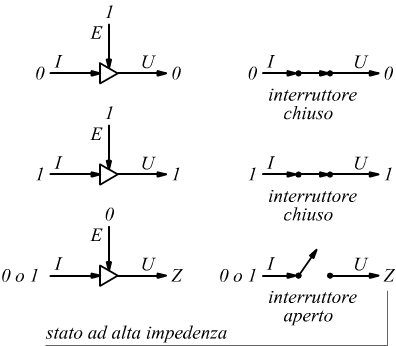

Buffer a tre stati

Negli schemi precedenti appare un simbolo sconosciuto di forma triangolare, si tratta del three-state-buffer (buffer a tre stati) un nuovo tipo di porta, usato prevalentemente per l'interfacciamento di didspositivi digitali. Il tipico banco di memoria ha un solo bus, usato sia in lettura che in scrittura. Quindi si può eseguire una sola operazione alla volta, lettura oppure scrittura; è comunque possibile implementare un bus bidirezionale che consenta la NON interferenza fra le uscite e le entrate alla memoria.

Il three-state-buffer è un dispositivo elementare modellabile come un contatto

in una delle tre possibili condizioni:

● in stato di bassa impedenza consente di

avere in uscita o il livello alto (1) o il livello basso (0)

● in stato di alta impedenza (Z) isola elettricamente

l'uscita.

Quando un apposito ingresso di controllo E (Enable) vale 0, il gate forza lo stato di alta impedenza Z.

il funzionamento di un buffer a tre stati è illustrato negli schemi seguenti:

L'importante è non confondere il buffer a tre stati con altre porte logiche come le porte AND oppure OR

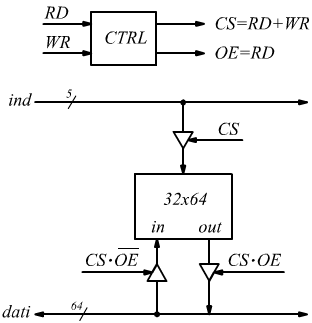

il three-state-buffer risulta essere molto utile per l'organizzazione della memoria in banchi, in modo particolare, può essere usato dalla logica di controllo per pilotare l'ingresso CS (Chip Select) del banco di memoria da selezionare. Il dispositivo di controllo per l'accesso ad una memoria bidirezionale dovrà distinguere tra le due operazioni RD (Read) e WR (Write) cioè, leggere o scrivere in in blocco di memoria. Queste due variabili (mai simultaneamente attive) dovranno essere poste in ingresso all'unità di controllo. In uscita ci saranno i terminali di CS e di OE (Output Enable). Ovviamente quando OE=1 il bus funziona in lettura (dato in uscita dalla RAM) quando OE=0 il bus funziona in scrittura (dato in ingresso alla RAM). La relazione tra ingressi ed uscite di questo blocco combinatorio che permette di gestire il traffico di dati in scrittura ed in lettura nella RAM sarà:

CS=RD+WR

OE=RD

Vediamo alcuni esempi :

Banco di memoria 32x64

Quando CS=0 il componente è isolato

con CS=1 ed OE=1 il bus funziona in lettura

con CS=1 ed OE=0 il bus funziona in scrittura

ovviamente il bus degli indirizzi è di 5bit (25=32) il bus dati è di 64bit perché tale è la dimensione della parola.

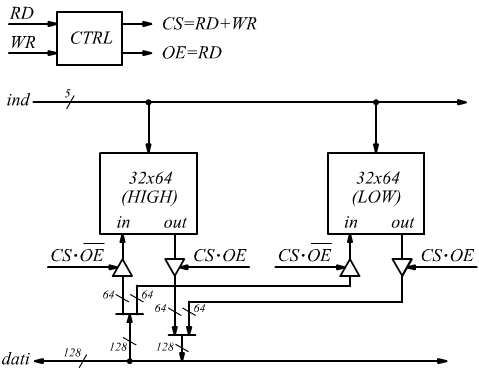

Espansione di parola

Banco di memoria da 32x128

implementato con 2 componenti da 32x64.

qui la memoria rimane a 32 righe, quindi, sono sempre necessarie 5 linee per il bus degli indirizzi.

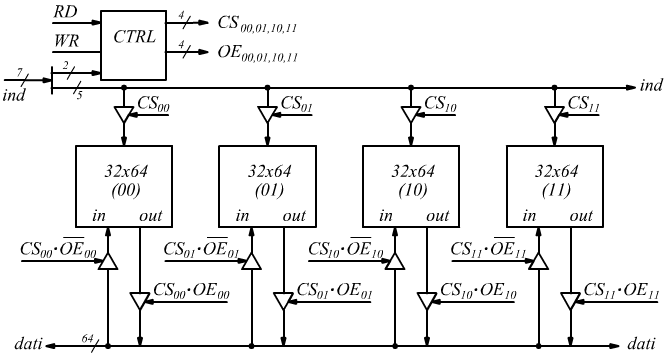

Espansione di riga

Banco di memoria da 128x64

implementato con 4 componenti da 32x64.

per raggiungere le 128 righe occorre disporre di 7 linee per il bus degli

indirizzi (27=128). I due bit più pesanti selezionano il banco

di memoria da attivare.

Esempi di funzionamento sono i seguenti:

Espansione di parola e di riga

Banco di memoria da 64x128

implementato con 4 componenti da 32x64.

per individuare le 64 righe di memoria occorrono 6 linee per il bus degli indirizzi (26=64) il bit più pesante individua il CS da attivare.

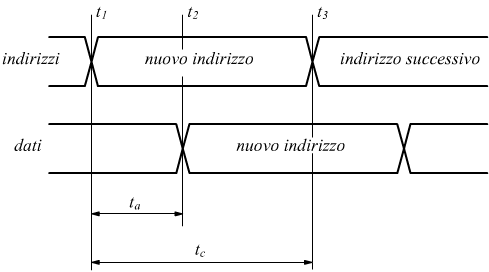

Temporizzazioni

I principali parametri che riguardano la velocità di funzionamento e quindi

le caratteristiche dinamiche delle memorie sono: il tempo di accesso in

lettura ta che è l'intervallo di tempo che passa tra l'istante

in cui viene applicato un certo indirizzo e l'istante in cui il relativo

dato è reso disponibile in uscita.

Il tempo di ciclo tc è invece il reciproco della frequenza con

cui possono essere variati gli indirizzi sugli ingressi della memoria e

dunque, specifica la frequenza massima con cui si può accedere alla memoria

stessa

Memorie ROM

Le memorie ROM sono memorie sola lettura (Read Only Memory) ad accesso casuale. Pur avendo un settore di impiego molto minore di quello delle RAM, esse occupano un settore strategico in quanto non sono volatili e sono indispensabili in tutti quei sistemi nei quali è necessario che il contenuto della memoria permanga inalterato nel tempo o per conservare dati elaborati che non devono andare perduti quando viene tolta l'alimentazione elettrica.

La fase di scrittura iniziale dei dati in una ROM è chiamata programmazione

ed è realizzata in base alle specifiche fornite dal costruttore. Per questo

motivo il costo iniziale di questo dispositivo è relativamente alto, ma

si riduce notevolmente man mano che aumentano i quantitativi prodotti.

Un altro svantaggio di questo tipo di dispositivo è la presenza di tempi

piuttosto lunghi che intercorrono tra la progettazione del dispositivo e

la sua effettiva realizzazione. Per questo motivo sono stati realizzati

e posti in commercio dei dispositivi programmabili dall'utente chiamati

PROM (Programmable Read Only Memory). Le PROM vengono programmate tramite

appositi dispositivi programmatori (programmer). Una volta programmata,

la PROM come la ROM non può più essere modificata o riprogrammata.

Le EPROM (Erasable PROM) sono memorie di sola lettura delle quali è possibile effettuare la cancellazione totale e la successiva riprogrammazione che viene effettuata tramite gli stessi dispositivi usati per programmare le PROM. La cancellazione della EPROM viene effettuata esponendo la zona di silicio su cui sono realizzate le celle di memoria a radiazione ultravioletta per almeno un tempo di circa 20 minuti. La cancellazione può essere solo complessiva e non può essere selettiva. Per permettere l'irradiazione, le PROM vengono confezionate all'interno di un contenitore ceramico dotato di una finestrella di quarzo trasparente ai raggi ultravioletti.

Una successiva evoluzione è stata la realizzazione delle EEPROM (Electricaly Erasable PROM) dette anche E2PROM : dispositivi cancellabili per mezzo di impulsi elettrici. Questo comporta che le EEPROM possono essere cancellate e riprogrammate senza nemmeno essere smontate dalla scheda elettronica sulla quale si trovano. La cancellazione è selettiva e può riguardare una singola locazione di memoria, un blocco di locazioni oppure tutta la memoria.

La cella di memoria di una EEPROM è più complessa di quella di una EPROM

perchè contiene due transistor invece che uno, dunque le prime sono caratterizzate

da una scala di integrazione minore delle seconde.

Un tipo di EPROM con caratteristiche intermedie tra EPROM ed EEPROM è la

memoria FLASH sviluppata nel 1987 da INTEL.

La cella di una memoria FLASH è costituita da un solo transistor come la

EPROM. Lo svantaggio che si ha è che la cancellazione può essere solo globale

o per settori; la cancellazione di una singola locazione di memoria non

è permessa.

Un tipico impiego delle memorie FLASH è la realizzazione delle Memory Card

dotate di formati diversi che possono contenere centinaia di Mbyte di memoria

FLASH; esse possono essere usate in sostituzione dei dischi rigidi dei computer

portatili, all'interno di telefoni cellulari o macchine fotografiche.

edutecnica

edutecnica