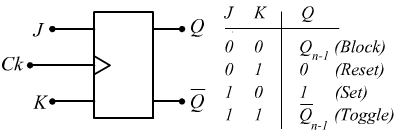

Flip-Flop JK edge-triggered

E' la forma più comune di memoria in grado di immagazzinare un bit.

Possiede due stati stabili che si mantengono indefinitivamente nel tempo

se non intervengono cause esterne a modificarli, per tale ragione il flip-flop

è classificato come dispositivo bistabile.

In genere nei sistemi digitali, le operazioni vengono eseguite sotto il

controllo di un generatore di onda quadra a frequenza fissa (dispositivo

astabile) con duty cyle del 50% (rapporto ON/OFF) detto clock. Si parla

così, di clocked logic o logica temporizzata. Il compito del clock è quello

di controllare la temporizzazione dei dispositivi logici e di regolarne

la velocità di esecuzione oltre a quello di sincronizzare tutte le operazioni

del sistema digitale.

Il nome edge-triggered sta a significare che le eventuali commutazioni

possono verificarsi solo in presenza del segnale di clock, in particolare,

in corrispondenza dei fronti di salita oppure dei fronti di discesa di tale

segnale.

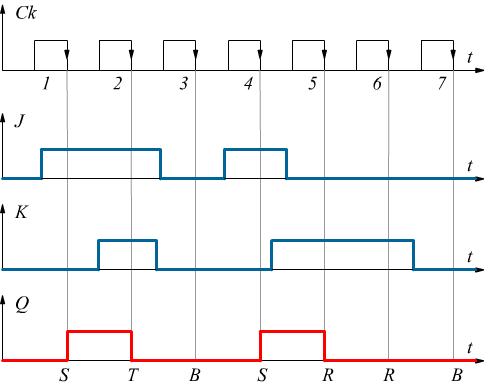

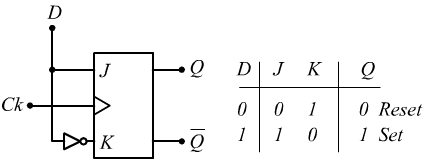

Nell'esempio in alto è riportato il principio di funzionamento di un FF-JK

a logica positiva (commutazioni sui fronti di salita del clock). Come si

nota se:

• J=1 e K=0 si ha Q=1 ed è la condizione di SET

• J=0 e K=1 si ha Q=0 ed è la condizione di RESET

• J=0 e K=0 l'uscita Q riconferma lo stato in cui si trovava l'uscita

prima del fronte di salita dell'impulso di clock, ed è la condizione di

BLOCK

• J=1 e K=1 l'uscita Q commuta rispetto allo stato in cui si trovava

l'uscita prima del fronte di salita dell'impulso di clock, ed è la condizione

di TOGGLE (commutazione rispetto allo stato precedente).

Questo dispositivo può essere costruito con porte a logica NAND come

nel caso dei flip-flop SR;

la differenza fondamentale è che il latch

SR non è triggerato da un segnale di clock.

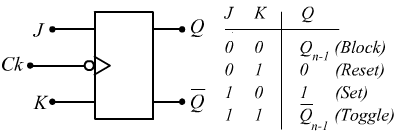

Qui sotto è riportato un FF-JK a logica negativa che commuta solo in corrispondenza

dei fronti di discesa dell'impulso di clock.

Che si tratti di un FF a logica negativa lo si riconosce dal pallino (di

negazione) all'ingresso di clock.

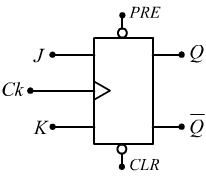

Vengono definiti ingressi sincroni, gli ingressi che hanno il controllo

diretto dell'uscita del bistabile quando è presente il clock, cioè gli

ingressi J e K.

Sono detti ingressi asincroni eventuali ingressi in aggiunta a

quelli sincroni. Questi ingressi sono in grado di influenzare le

uscite del FF indipendentemente dalla presenza o meno del segnale

di clock.

Si tratta degli ingressi di CLEAR e di PRESET, in grado di porre,

rispettivamente, a 0 e a 1 l'uscita Q indipendentemente dagli ingressi

JK e dal clock.

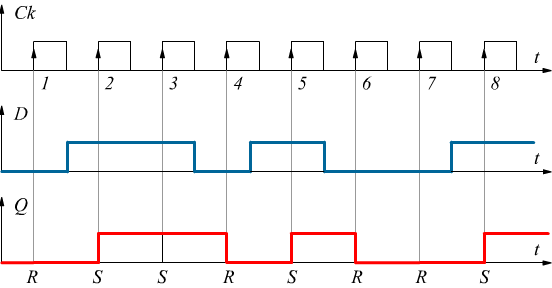

Flip-Flop D (data) o latch

Deve essere osservata l'equazione D = J = K .

Osservando la tabella degli stati, si nota come l'uscita Q cambia stato

e assume lo stato logico presente all'ingresso D solo durante gli impulsi

di clock (fronti di salita o di discesa a seconda che sia a logica positiva

o negativa).

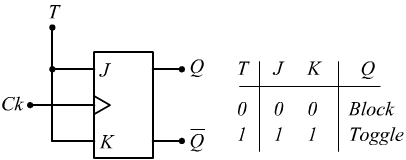

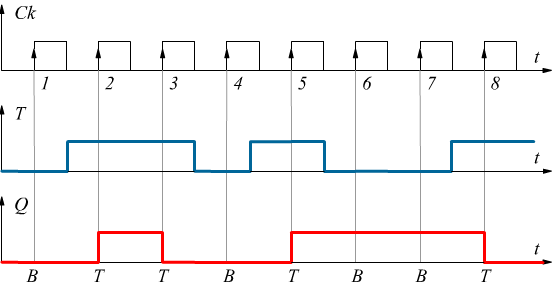

Flip-Flop T (toggle)

Componente particolarmente usato per la costituzione di contatori si ottiene ponendo T=J=K. In pratica, il FF commuta rispetto allo stato precedente se l'ingresso T=1 altrimenti, riconferma lo stato logico precedente se T=0.

edutecnica

edutecnica