Alea statica

Il termine alea significa rischio. Fin qui, abbiamo fatto l'ipotesi che

i circuiti costruiti con le porte logiche siano ideali, cioè che rispondano

istantaneamente ai segnali di ingresso con un tempo di propagazione nullo.

Questo però può essere vero solo in teoria, perchè in pratica (come in tutte

le cose) può andare diversamente.

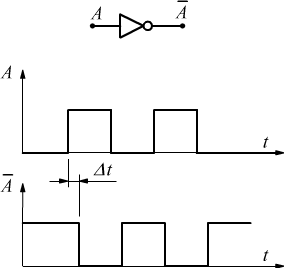

Ad esempio, per una semplicissima porta NOT,la risposta dell'uscita avviene

con un ritardo Δt rispetto al segnale di ingresso.

In pratica, ai componenti reali, sono associati dei ritardi, che possono

provocare errati funzionamenti della rete combinatoria che realizza la funzione

booleana, sopratutto all'aumentare della frequenza di lavoro imposta dal

clock.

Il problema delle alee che non esiste in teoria deve quasi sempre essere

affrontato e risolto quando si passa alla realizzazione concreta di un circuito.

Supponiamo di avere una funzione logica minima associata alla ricopertura

della mappa riportata.

Se realizziamo questa funzione usando per semplicità gli interruttori

(ON=1 e OFF=0). La corrente I rappresenta la variabile dipendente, ed essa

potrà scorrere nel circuito solo se uno dei due rami del parallelo risulta

chiuso tramite i relativi contatti.

Nello schema (a) qui sotto riportato è rappresentata la funzione per A=B=C=1.

In questo caso la corrente può fluire nel ramo 2, perchè ci sono i contatti

A e C chiusi e la funzione Y di uscita vale 1. Notiamo però, che nella rete

ci sono due contatti A e A che sono uno il negato

dell'altro, cioè sono realizzati da due contatti dello stesso interruttore,

uno normalmente aperto e l'altro normalmente chiuso.

Supponendo, ora, di passare dalla configurazione 111 alla 011 si otterrebbe lo schema (b) in questo caso la corrente fluisce attraverso il ramo 1.

Accade però che non è possibile non è possibile provocare simultaneamente l'apertura di A (da 1 a 0) e la chiusura di A (da 0 a 1).

Durante la commutazione si possono verificare due casi:

● A chiude prima che A apra; in questo caso A ed A restano entrambi chiusi, e per un breve periodo di tempo tutti e due i rami porteranno corrente. Quando A apre, la corrente fluirà solo nel ramo 1 al nodo di uscita, non si verifica quindi alcuna interruzione ed Y rimane sempre ad 1 durante la commutazione come nello schema (I).

● A apre prima che A chiuda; in questo caso per un breve periodo di tempo Δt, entrambi i rami risultano aperti e si avrà perciò, interruzione del flusso di corrente in uscita, Y rimane a 0 finchè A non ha chiuso, poi torna normalmente ad 1 come nello schema (II). Si ha quindi la generazione di uno zero spurio (non desiderato). Questo fenomeno è quello che va sotto il nome di alea statica.

Esiste la possibilità di le alee statiche di tipo 0 (cioè zeri spuri)

tutte le volte che sulla mappa di Karnaugh si passa da un 1 di una cella

a quello di un'altra cambiando la ricopertura.

Cioè, si ha un'alea statica quando si presentano due 1 adiacenti non ricoperti

dalla stessa ricopertura. Infatti in questo caso l'1 deve essere fornito

da due porte diverse che possono non commutare simultaneamente; nel nostro

caso l'alea è determinata dalla transizione 111 → 011.

Per eliminare le alee dobbiamo realizzare la funzione in forma ridondante (non minima) aggiungendo una ricopertura che contenga la transizione aleatoria. Nell'esempio che abbiamo visto, bisogna aggiungere la ricopertura mostrata nel disegno seguente

ponendo il termine ridondante BC; risulterà la funzione

![]() e

non sarà più minima

e

non sarà più minima

Verifichiamo col circuito degli interruttori come una ricopertura di Y in questa forma elimini il pericolo di malfunzionamenti nella transizione 111 → 001. Si nota che l'uscita Y=1 viene fornita in condizioni stazionarie, dai rami della rete 1 e 3. Anche se durante la transizione A e A si trovano contemporaneamente aperti, esiste sempre il ramo 3 che permette il flusso di corrente, e la funzione Y rimane costantemente ad 1.

La presenza di un'alea può anche essere messa in rilievo tramite l'analisi del circuito logico che nel seguente disegno si riferisce alla Y=AC+AB

Consideriamo la situazione A=B=C=1, A=0,

all'uscita della porta AND-1 ci sarà un 1 e quidi Y=1.

Supponiamo ora che si verifichi una transizione di A da 1 a 0 (ci stiamo

spostando dallo stato 111 allo stato 011); dato che il negatore in ingresso

alla AND-2 provoca un ritardo, l'uscita della AND-1 andrà a 0 prima che

la AND-2 vada ad 1, si genera, quindi un'alea di tipo 0.

La transizione opposta (001 → 111) non crea invece nessun segnale spurio.

L'alea statica si evita passando al seguente schema

Le alee possono anche essere di tipo 1, se provengono da sintesi OR-AND, nella seguente mappa è mostrata una funzione con ricopertura che può dar luogo alla formazione di un 1 spurio, a causa della transizione 001 → 101 degli ingressi ABC.

Si conclude che una rete combinatoria non presenta alee statiche se ogni coppia di 1 adiacenti (o di 0) è coperta da almeno un sottogruppo comune. La necessità di eliminare le alee, ed aumentare l'affidabilità del circuito, aggiunge porte logiche ridondanti, ed aumenta la complessità ed il costo del progetto.

edutecnica

edutecnica