Registri

Il flip-flop, già visto in precedenza, rappresenta lelemento minimo con cui costruire una rete sequenziale perché già in grado di memorizzare 1 bit di informazione. Quando è necessario immagazzinare più bit di informazione bisogna ricorrere a strutture più elaborate che prendono il nome di registri.

Il registro,dovrà essere formato da più flip-flop opportunamente collegati. Un registro rappresenta un sistema di memoria non permanente, che acquisisce informazioni in forma binaria. Si tratta infatti, di una memoria volatile i cui dati si perderebbero qualora mancasse la corrente elettrica. Possono essere costruiti attraverso varie configurazioni circuitali con un prefissato numero n di flip-flop, con il terminale di clock e di reset comuni; essi, possono in questo modo, essere in gado di memorizzare n bit.

L'elemento fondamentale dei registri può essere considerato il flip-flop di tipo D che costituisce, a tutti gli effetti, una cella elementare di memoria. Qui sotto riportiamo il simbolo e la tabella della verità di un flip-flop JK edge triggered a logica positiva (commuta in corrispondenza dei fronti di salita del segnale di clock) e si mostra, come da esso può essere ottenuto un flip-flop D con le corrispondenti tabelle della verità.

I registri vengono usati in molti campi di applicazione, in genere quando bisogna mantenere dei dati in memoria dei dati per un certo periodo di tempo, in attesa che altri dispositivi abbiano completato le loro elaborazioni. Ad esempio, le operazioni tipiche di una ALU all'interno di un microprocessore, sono di norma effettuate su operandi contenuti in registri ed i risultati ottenuti vengono a loro volta immagazzinati in registri.

Un registro deve possedere le seguenti caratteristiche:

• acquisire l'informazione, con la

possibilità di caricare i dati previsti;

• mantenere l'informazione per il

tempo stabilito;

• restituire l'informazione; deve

la possibilità di restituire i dati memorizzati anche se in taluni casi,

la fase di lettura coincide la distruzione dell'informazionee contenuta

nel registro .

L'appellativo esatto sarebbe 'registri a scorrimento' (shift register): il modo più semplice per costruirli è quello di collegare una catena di flip-flop con clock e reset comuni; in essi, i bit di informazione possono scorrere verso destra o verso sinistra; come disegnato qui sotto.

I dati digitali che devono essere memorizzati, possono presentarsi agli ingressi del dispositivo in forma seriale o parallela. Nel primo caso tutti i bit di una parola vengono trasferiti lungo un'unica linea in sequenza ordinata, un bit dopo l'altro (in trasmissione seriale). Il trasferimento in parallelo, invece, richiede tante linee quanti sono i bit della parola.

Registri SISO e SIPO

Con queste sigle intendiamo

SISO : serial input - serial output ;

SIPO : serial input - parallel output ;

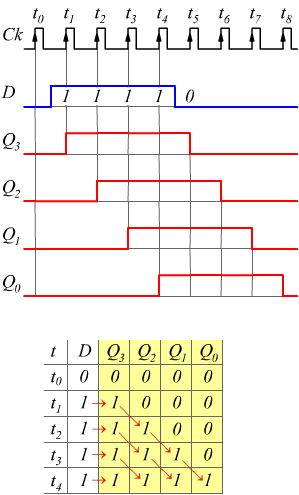

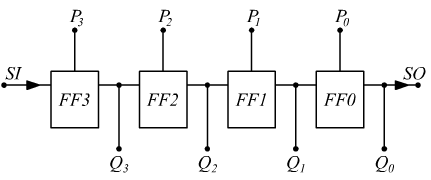

Nel disegno seguente, viene rappresentato lo schema di un registro a scorrimento costituito da quattro flip-flop di tipo D collegati in cascata e comandati da un clock comune.

Ad ogni fronte di salita del clock il dato presente sull'ingresso generico

Di connesso all'uscita Qi viene trasferito all'uscita

Qi-1.

Se ad esempio il registro si trova nella stato Q3Q2Q1Q0=0000

con D=D3=1, dopo la prima transizione di clock, sulle uscite

si avrà la configurazione Q3Q2Q1Q0=1000;

dopo la seconda transizione di clock si avrebbe Q3Q2Q1Q1=1100;

alla terza si averebbe 1110 e alla quarta 1111. Quindi dopo quattro impulsi

di clock, il dato D=1 risulta caricato in tutti gli elementi del registro.

Questo processo viene rappresentato qui sotto

Si nota come lo scorrimento implica la perdita dei dati precedentemente caricati. Questo apparato, permette, dunque, la memorizzazione di una parola a 4 bit in modo seriale; infatti, se la lettura viene effettuata prelevando i bit che in sincronismo col segnale di clock si presentano sull'uscita Q3 si ottiene un dato in uscita in formato seriale (SISO=serial input - serial output). Per la precisione un registro SISO richiede 4 impulsi di clock per la scrittura e 4 impulsi per la lettura per un tempo teorico di 8Tck ; la lettura è distruttiva.

Una volta effettuato il caricamento i 4 bit memorizzati nel registro, possono anche essere prelevati simultaneamente sulle uscite Q3Q2Q1Q0 ed in tal caso la lettura avverrà (in modo non distruttivo) in un tempo 4Tck in formato parallelo (SIPO=serial - parallel output).

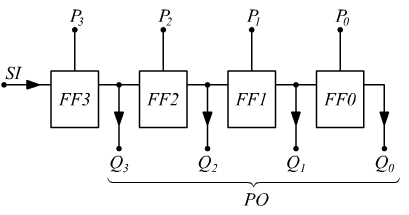

Registri PISO e PIPO

Nello schema qui sotto disegnato, il registro effettua il caricamento dei dati in forma parallela. I quattro bit della parola da memorizzare vengono applicati ai morsetti di ingresso P3P2P1P0; se l'ingresso di controllo PE (parallel enable) è attivo alto, viene dato il consenso al caricamento. In questo modo i dati sui terminali Pi attraversano le porte AND-OR e si presentano sugli ingressi Di.

Dopo il primo fronte di salita del segnale di clock i dati sono disponibili anche sulle uscite Q3Q2Q1Q0. Si può intuire che durante questa fase lo stato dei terminali Pi deve restare stabile fin tanto che l'ingresso PE è abilitato (alto) per evitare la scrittura di dati errati. Terminato il processo di scrittura PE può essere disabilitato e i dati sono disponibili ad essere prelevati in formato parallelo sulle uscite Qi (PIPO=parallel input - parallel output).

In questo caso è richiesto un comando di scrittura ed un comando di lettura, per un tempo totale non dipendente dal clock, quindi, estremamente esiguo; la lettura non è distruttiva.

E' sottinteso che finora vi sia stato un solo ed unico impulso di clock, perché quelli successivi sortirebbero l'effetto di trasferire progressivamente verso destra, i bit memorizzati, cioè, verso l'uscita seriale Q0. Durante i quattro cicli di clock che seguono il comando di memorizzazione, dunque, si realizza un procedimento di scrittura di tipo PISO=parallel input - serial output.

In questo caso, si richiedono 4 impulsi di clock per la lettura ed un solo comando per la scrittura per un tempo operativo teorico di 4Tck . La lettura è distruttiva.

Comando parallelo

A parte queste configurazioni standard bisogna sempre ricordare che il modo più rapido per caricare un registro a 4 bit consiste nell'usare il terminale di preset di cui è dotato ogni singolo FF.

In questo caso, tutti i FF vengono istantaneamente caricati con la configurazione di bit che si presenta agli ingressi di preset (che sono indipendenti dal clock) e istantaneamente gli stessi dati sono presenti all'uscita; inoltre, la lettura parallela ha il vantaggio di non distruggere l'informazione mentre la lettura seriale la distrugge ed implica un tempo di lettura di 4Tck. Per contro è necessaria una piedinatura maggiore a causa della necessità delle 4 linee di accesso, inoltre nel disegno abbiamo inserito il comando di clear (CLR che dovrebbe essere sempre presente) che consente (è attivo basso) un eventuale azzeramento asincrono delle uscite dei FF.

Registro ad anello

Ipotizziamo di avere un registro a scorrimento a 4 bit preventivamente caricato e supponiamo di stabilire un collegamento tra il primo e l'ultimo FF della catena.

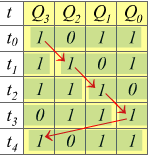

Il clock diventerà operativo solo quando En=1 (alto). I fronti attivi provocano lo scorrimento dell'informazione, la quale, oltre a presentarsi in uscita in modo seriale, si ripresenta in ingresso con i bit esattamente nella stessa successione con la quale sono stati caricati. Si può immaginare che dopo 4 impulsi di clock il registro presenta la stessa configurazione originaria che in questo modo non è andata perduta. Il comportamento dello scorrimento ad anello è qui a sinistra riportato.

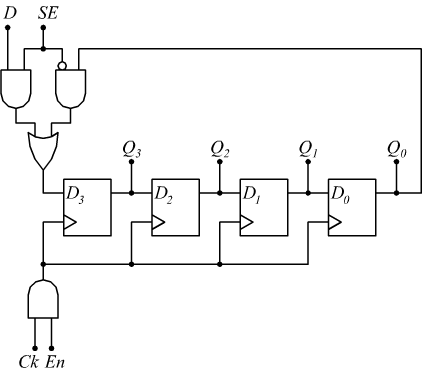

Durante l'operazione di scorrimento ad anello, l'ingresso seriale D deve essere disabilitato. Il comando di selezione può essere ottenuto impiegando due porte AND ed una OR secondo lo schema qui riportato.

Lo stato del comando di abilitazione SE(serial enable) fornisce il consenso al caricamento del dato proveniente dai due ingressi D oppure Q0.

SE=1 è abilitato il caricamento da D

SE=0 è abilitato il caricamento dall'uscita seriale Q0

Il modo di operare di questo dispositivo si deduce anche dalla sua funzione di uscita

![]()

Qui sotto è disegnato lo schema completo del registro ad anello completo del gruppo di selezione; questo tipo di registro consente la lettura seriale non distruttiva del dato. Esso permette di conservare un dato per tempi anche molto lunghi, multipli di 4Tck per poi disporne in uscita con un ritardo programmato.

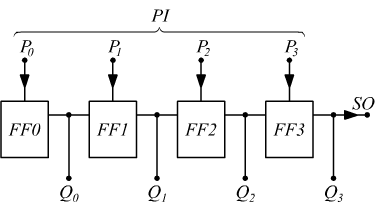

Registri a scorrimento diretto ed inverso

I tipi di registri finora visti funzionano al ritmo imposto dal clock, in senso diretto da sinistra verso destra. Ci può essere la necessità di far scorrere il dato da destra verso sinistra in senso inverso. Per ottenere questo effetto è sufficiente invertire l'ordine di successione dei FF da 3-2-1-0 a 0-1-2-3.L'ingresso seriale D deve essere collegato a D0 l'uscita deve essere D3.

In modo generale è possibile realizzare un registro completo che possa

effettuare ingresso ed uscita seriali, con scorrimento sia a sinistra che

a destra ![]() questo

dispositivo è reperibile anche su circuiti integrati secondo lo schema:

questo

dispositivo è reperibile anche su circuiti integrati secondo lo schema:

La predisposizione ![]() avviene

con presenza di un segnale di selezione 0 oppure 1 sulla linea corrispondente;

questa operazione è eseguita usando il gruppo di selezione descritto prima.

Quando

avviene

con presenza di un segnale di selezione 0 oppure 1 sulla linea corrispondente;

questa operazione è eseguita usando il gruppo di selezione descritto prima.

Quando

![]() è

attivo R e lo scorrimento è verso destra

è

attivo R e lo scorrimento è verso destra

![]() è

attivo L e lo scorrimento è verso sinistra

è

attivo L e lo scorrimento è verso sinistra

La porta AND relativa all'abilitazione ![]() a

destra è connessa all'uscita del FF precedente (k+1); la porta AND relativa

all'abilitazione versi sinistra è connessa del FF seguente (k-1). la funzione

logica di ciascun ingresso è dunque

a

destra è connessa all'uscita del FF precedente (k+1); la porta AND relativa

all'abilitazione versi sinistra è connessa del FF seguente (k-1). la funzione

logica di ciascun ingresso è dunque

![]()

edutecnica

edutecnica